Introduction

In this project, I demonstrate a complete FM demodulation system implemented on a Spartan-7 FPGA, where a 10.7 MHz FM-modulated RF signal is digitized and fully recovered in the digital domain. The system uses an ADC1173 sampling at 10 MHz, intentionally operating in a bandpass undersampling regime to directly alias the RF input into an intermediate frequency (IF), eliminating the need for a traditional analog mixer stage.

After sampling, the aliased IF signal is digitally downconverted to baseband using quadrature mixing with a DDS-generated local oscillator. This process preserves both amplitude and phase information, which is essential for accurate FM demodulation.

The resulting complex baseband signal is then processed through a multistage digital filtering and decimation chain using FIR filters, reducing the sampling rate while removing out-of-band spectral components and improving signal quality.

Finally, the system implements a discrete-time FM demodulator based on phase differentiation, enabling efficient recovery of the original modulating (audio) signal using FPGA-friendly arithmetic operations.

Overall, this project demonstrates how a complete RF receiver chain can be implemented entirely in the digital domain using a combination of undersampling theory, digital downconversion, multirate signal processing, and FPGA-based DSP techniques.

—

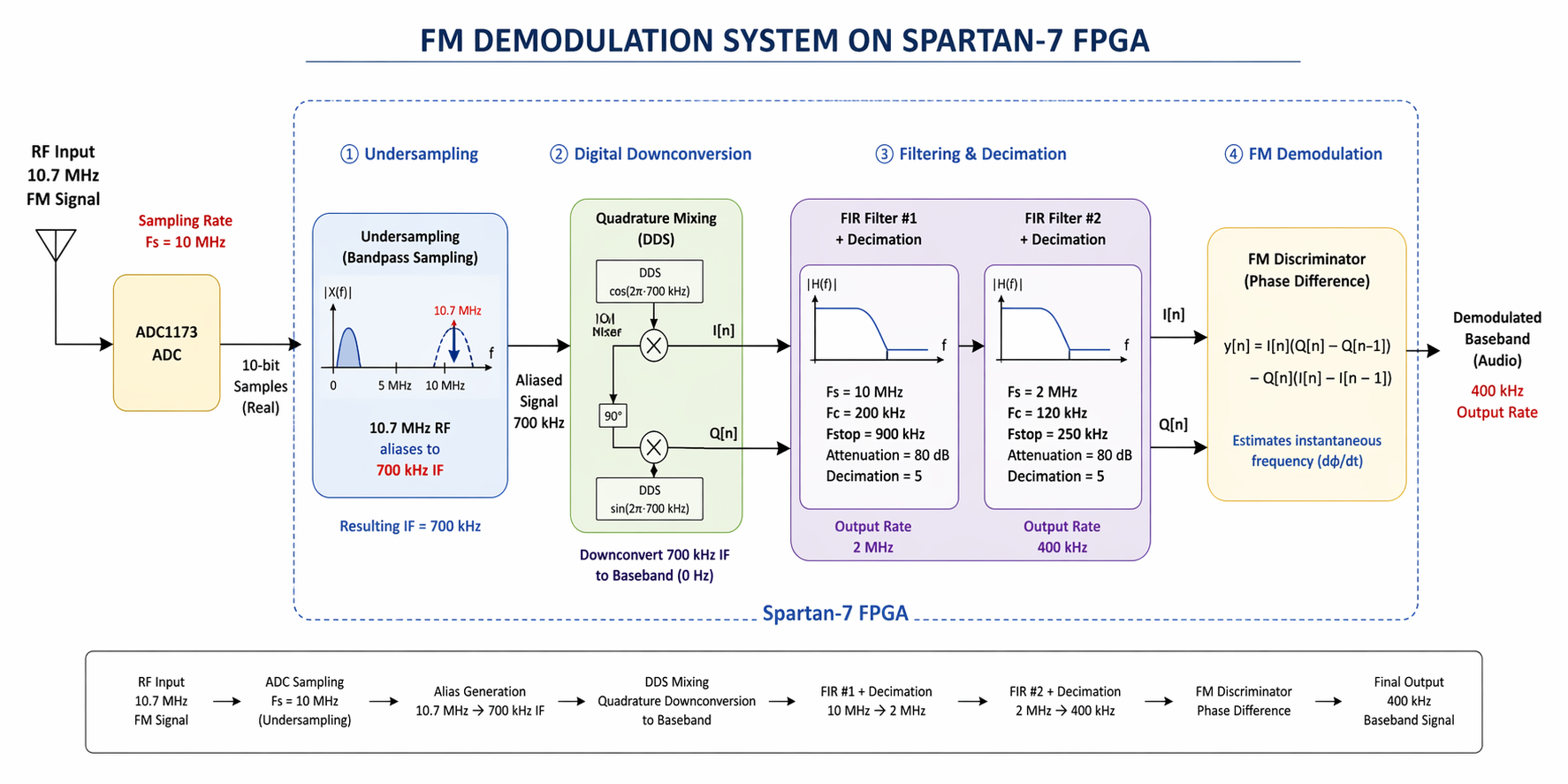

FM Demodulation System Block Diagram

Below is a block diagram of the FM demodulator designed. All design specifications are also included in the diagram.

—

Digital Implementation

1. Undersampling Principle (Bandpass Sampling)

Normally, a 10.7 MHz signal would require a sampling rate above 21.4 MHz. However, in bandpass sampling (undersampling), a band-limited RF signal can be sampled below the Nyquist rate as long as:

- The signal bandwidth is narrow enough

- Aliased spectral images do not overlap

Instead of preserving absolute frequency, undersampling preserves the information content of the signal. After sampling, the signal folds into the first Nyquist zone, producing an aliased intermediate frequency (IF).

Given:

Fs = 10 MHz

FRF = 10.7 MHz

Resulting IF ≈ 700 kHz

This occurs because the spectrum is mirrored around multiples of the sampling frequency. The alias frequency is given by:

fIF = | fRF − N · Fs |

For N = 1:

fIF = |10.7 MHz − 10 MHz| = 0.7 MHz

2. Digital Downconversion (DDC)

After sampling, the signal is centered at 700 kHz IF instead of baseband. To recover the original modulation, the FPGA performs digital mixing.

2.1 Quadrature Mixing Using DDS

The 700 kHz aliased signal is multiplied with a quadrature local oscillator (LO) generated by a DDS:

- cos(2π · 700 kHz)

- sin(2π · 700 kHz)

This produces:

- In-phase component I[n]

- Quadrature component Q[n]

This step shifts the signal from IF (700 kHz) down to baseband (0 Hz) while preserving phase information required for FM demodulation.

3. Digital Filtering and Decimation Chain

After downconversion, the signal is still sampled at 10 MHz. FIR filtering and decimation are used to reduce data rate and remove unwanted spectral components.

3.1 First FIR Filter + Decimation

- Sampling rate: 10 MHz

- Cutoff frequency: 200 kHz

- Stopband frequency: 900 kHz

- Attenuation: 80 dB

- Decimation factor: 5

Purpose:

- Remove high-frequency mixing products

- Keep only near-baseband FM information

- Reduce sampling rate

Output rate: 2 MHz

3.2 Second FIR Filter + Decimation

- Sampling rate: 2 MHz

- Cutoff frequency: 120 kHz

- Stopband frequency: 250 kHz

- Attenuation: 80 dB

Purpose:

- Further clean the baseband FM signal

- Remove residual high-frequency noise

- Prepare signal for FM demodulation stage

4. FM Demodulation in FPGA

After filtering, the signal exists in complex form:

- I[n] (in-phase)

- Q[n] (quadrature)

4.1 Discrete FM Discriminator

y[n] = I[n](Q[n] − Q[n−1]) − Q[n](I[n] − I[n−1])

4.2 Function

This computes phase change over time without using arctangent operations. It approximates:

d/dt (tan⁻¹(Q/I))

4.3 Advantages

- No CORDIC required

- Efficient FPGA implementation

- High-speed operation

- Robust to amplitude variations

5. Final Output

After the second decimation stage, the final output rate is:

400 kHz

This signal represents the recovered baseband audio/modulating signal using:

- Undersampling

- Digital downconversion

- FIR filtering

- Phase-based FM demodulation

6. Conclusion

An FM-modulated IF signal was successfully demodulated on a Spartan-7 FPGA using Xilinx IP cores including DDS and FIR filters. The 5 kHz message signal is recovered and displayed on the scope.

In the next project, a full digital FM radio implementation on FPGA will be demonstrated.

Author: Farid M